# **SP973T8**

# 30MHz 8-BIT FLASH ADC (TTL/CMOS OUTPUTS)

The SP973T8 is a wideband, full flash analog-to-digital converter that requires no preceding sample and hold. The device contains a full 8-bit D-type latch which ensures that the 8 TTL/CMOS outputs are accurately registered and have a good data valid time at high clock speeds.

IIII GEC PLESSEY

SEMICONDUCTORS

Operating from a single +5 volt supply the device is capable of conversion rates well in excess of 30MHz and its wideband input allows signals with frequencies up to the Nyquist limit to be digitised with high accuracy. An internal bandgap voltage regulator gives low DC drift over a wide operating temperature range.

The SP973T8 is designed for applications where power consumption and package size is at a premium.

#### FEATURES

- Flash Converter, No Sample and Hold Required

- Wideband Analog Input 70MHz, 3dB (Typ.)

- Low Power Consumption (600mW Typ.)

- Latched TTL/CMOS Compatible Outputs

- No Missing Codes Guaranteed

- Designed for Wideband Operation

- Single 5V Supply

- Production Tested at 30MHz

#### **ORDERING INFORMATION**

SP973T8 C DP (Commercial - Plastic DIL package)

#### **APPLICATIONS**

- Studio Quality Video

- DBS Broadcast Video

- High Resolution TV

- Nucleonics

- Radar

- Computing

# **ABSOLUTE MAXIMUM RATINGS**

| Supply voltage, Vcc   | 7V              |

|-----------------------|-----------------|

| Output Current        | 10mA            |

| Input Voltage, VIN    | Vcc             |

| Operating Temperature | 0°C to +70°C    |

| Storage Temperature   | -65°C to +150°C |

|                       |                 |

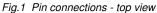

Fig.2 Internal block diagram

# SP973T8

# ELECTRICAL CHARACTERISTICS

These characteristics are guaranteed over the following conditions (unless otherwise stated):

$T_{amb} = 25^{\circ}C, V_{CC} = +5V \pm 0.25V$

Full temperature range =  $0^{\circ}C$  to  $+70^{\circ}C$

# DC CHARACTERISTICS

| Characteristic             | Symbol | Temp. | Test level | Value |      |         | Units | Conditions            |  |

|----------------------------|--------|-------|------------|-------|------|---------|-------|-----------------------|--|

| Characteristic             |        |       |            | Min.  | Тур. | Max.    | Units | Conditions            |  |

| Power Supply               |        |       |            |       |      |         |       |                       |  |

| Supply current             | lcc    | Full  | 4          | 100   |      | 140     | mA    |                       |  |

|                            |        | 25    | 1          | 110   | 120  | 130     | mA    |                       |  |

| Power dissipation          | PD     | Full  | 4          | 475   |      | 735     | mW    |                       |  |

|                            |        | 25    | 1          | 520   | 600  | 680     | mW    |                       |  |

| Analog Input               |        |       |            |       |      |         |       |                       |  |

| Input range                | VIN    | Full  | 4          | 1.8   |      | Vcc-0.7 | V     |                       |  |

| Input bias current         | lin    | 25    | 1          | 150   | 390  | 1100    | μA    | $V_{IN} = V_{RT}$     |  |

| 3dB bandwidth              | fзdb   | 25    | 4          |       | 70   |         | МНz   |                       |  |

| Input capacitance          | CIN    | 25    | 4          |       | 30   |         | pF    |                       |  |

| Reference Ladder           |        | -     |            |       |      |         |       |                       |  |

| Ladder resistance          | R⊳     | 25    | 1          | 325   | 440  | 550     | Ω     |                       |  |

| Ladder voltage (top)       | VRT    | Full  | 4          |       | 4.3  | Vcc-0.7 | V     |                       |  |

| Ladder voltage (bottom)    | Vrb    | Full  | 4          | 1.8   | 2.3  |         | V     |                       |  |

| Ladder offset (top)        | VRT0   | 25    | 5          |       | -4   |         | mV    |                       |  |

| Ladder offset (bottom)     | VRB0   | 25    | 5          |       | +3   |         | mV    |                       |  |

| Ladder temp. coeff.        | RTC    | Full  | 5          |       | 1.5  |         | Ω/°C  |                       |  |

| Clock Input                |        |       |            |       |      |         |       |                       |  |

| Logic '1' voltage          | ViH    | Full  | 4          | 2.75  | 4.3  | Vcc     | V     | A swing of 1V controd |  |

| Logic '1' current          | Пн     | 25    | 1          |       |      | 25      | μA    | A swing of 1V centred |  |

| Logic '0' voltage          | Vı∟    | Full  | 4          | 1.75  | 3.3  | Vcc-1.0 | V     | to the <u>CLK</u> pin |  |

| Logic '0' current          | lı∟    | 25    | 1          |       |      | 2       | μA    |                       |  |

| Digital Outputs            |        |       |            |       |      |         |       |                       |  |

| Logic '1' voltage          | Vон    | Full  | 4          | 3.3   |      |         | V     |                       |  |

|                            |        | 25    | 1          | 3.5   | 3.8  |         | V     | Linto Standard LS     |  |

| Logic '0' voltage          | Vol    | Full  | 4          |       |      | 0.4     | V     | ( TTL Load            |  |

|                            |        | 25    | 1          |       | 0.1  | 0.4     | V     | )                     |  |

| Static performance         |        |       |            |       |      |         |       |                       |  |

| Differential non-linearity | DNL    | Full  | 4          |       |      | ±1      | LSB   |                       |  |

|                            |        | 25    | 4          |       |      | ±0.5    | LSB   |                       |  |

| Integral non-linearity     | INL    | Full  | 4          |       |      | ±1      | LSB   |                       |  |

|                            |        | 25    | 4          |       |      | ±1      | LSB   |                       |  |

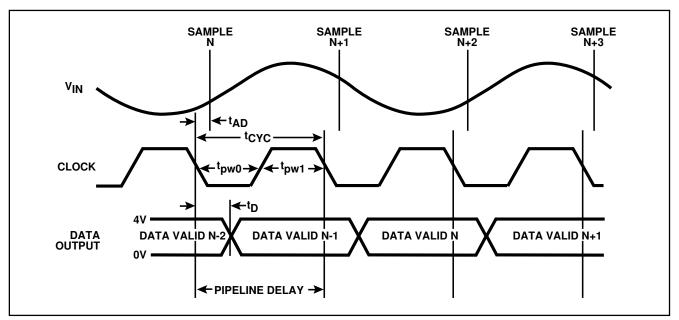

# AC CHARACTERISTICS (Refer to Fig.7)

| Characteristic             | Symbol <sup>-</sup> | Temp. | Test level | Value |                      |      | Units | Conditions            |

|----------------------------|---------------------|-------|------------|-------|----------------------|------|-------|-----------------------|

| Characteristic             |                     |       |            | Min.  | Тур.                 | Max. | Units | Conditions            |

| Clock min. high            | tPW1                | 25    | 4          | 10    |                      |      | ns    |                       |

| Clock min. low             | tpw0                | 25    | 4          | 10    |                      |      | ns    |                       |

| Max. conversion rate       |                     | Full  | 4<br>5     | 30    | 50                   |      | MHz   | AIN = 15MHz at FS     |

| Aperture delay             | tad                 | 25    | 5          |       | 3                    |      | ns    |                       |

| Output data delay          | t⊳                  | 25    | 4          |       | 7                    |      | ns    |                       |

| Output rise time           | t₽                  | 25    | 4          |       | 6                    |      | ns    |                       |

| output fall time           | t⊧                  | 25    | 4          |       | 8                    |      | ns    |                       |

| Dynamic Performance        |                     |       |            |       |                      |      |       | With FCLK = 30MHz     |

| Differential non-linearity | DNL                 | 25    | 1          | -0.85 | ±0.5                 | +1   | LSB   | AIN MAX = 10MHz at FS |

| Integral non-linearity     | INL                 | 25    | 1          |       | ±1                   | ±2   | LSB   | AIN MAX = 10MHz at FS |

| S/N ratio                  | SNR                 | 25    | 1          | 40.9  | 44.5                 |      | dBc   | AIN MAX = 1MHz at FS  |

|                            |                     |       | 4          |       | 44.1                 |      | dBc   | AIN MAX = 5MHz at FS  |

|                            |                     |       | 4          |       | 43.3                 |      | dBc   | AIN MAX = 10MHz at FS |

| Effective No. of bits      | ENOB                | 25    | 1          | 6.5   | 7.1                  |      | bits  | AIN MAX = 1MHz at FS  |

|                            |                     |       | 4          |       | 7.0                  |      | bits  | Ain мах = 5MHz at FS  |

|                            |                     |       | 4          |       | 6.9                  |      | bits  | AIN MAX = 10MHz at FS |

| Bit Error Rate             | BER                 | 25    | 4          |       | 1 in 10 <sup>9</sup> |      |       |                       |

# ELECTRICAL CHARACTERISTICS DEFINITIONS Analog Bandwidth

The analog input frequency at which the spectral power of the fundamental frequency, as determined by Fast Fourier Transform analysis is 3dB down on the DC level.

### Aperture Delay

The delay between the falling edge of the CLOCK signal and the instant at which the analog input is sampled.

### Bit Error Rate (BER)

The number of spurious code errors produced for any given input sinewave frequency. In this case it is the number of codes occuring outside the histogram cusp for a  $^{3}/_{4}$  F.S. sinewave.

# **Differential Non-Linearity (DNL)**

The deviation of any code width from an ideal 1LSB step.

# Effective Number of Bits (ENOB)

This is a measure of the dynamic performance and is calculated from the following expression.

SNR is the signal-to-noise ratio, in decibels, at the test frequency.

## **PIN DESCRIPTIONS**

#### Integral Non-Linearity (INL)

The deviation of the centre of each code from a reference line which has been determined by a least squares curve fit.

### **Output Data Delay**

The delay between the 50% point of the falling edge of the clock signal and the 50% point of any data output change.

#### **Reference Ladder Offset**

The voltage error at the ends of the resistor chain caused by the lead frame and bond wire.

#### Signal-to-Noise Ratio (SNR)

The ratio of the RMS signal amplitude to the RMS value of 'noise' which is defined as the sum of all other spectral components including harmonics but excluding DC with a full scale analog input signal.

### **Test Levels**

Level 1 - 100% production tested Level 2 - 100% production tested at 25°C and sample tested at specified temperatures Level 3 - Sample tested only Level 4 - Parameter is guaranteed by design and characteristics testing Level 5 - Parameter is a typical value only

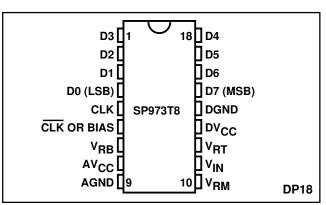

| Pin No.                                                                               | Function                                                                                                            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|---------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 2, 3, 4<br>5<br>6<br>7<br>8<br>9<br>10<br>11<br>12<br>13<br>14<br>15<br>16, 17, 18 | D3, D2, D1, D0<br>CLK<br><u>CLK</u><br>VRB<br>AVcc<br>AGND<br>VRM<br>VIN<br>VRT<br>DVcc<br>DGND<br>D7<br>D6, D5, D4 | <ul> <li>Output data bits 3, 2, 1, 0</li> <li>Clock input pin</li> <li>Clock threshold level pin</li> <li>Bottom of reference resistor chain</li> <li>5 Volt power to all circuitry except the TTL output</li> <li>Middle of reference resistor chain</li> <li>Analog input voltage pin</li> <li>Top of reference resistor chain</li> <li>\$ Volt power supply to the TTL output stage</li> <li>Most significant bit (output data bit 7)</li> <li>Output data bits 6, 5, 4</li> </ul> |

# **RECOMMENDED OPERATING CONDITIONS**

| Supply Voltage Vcc           | +5.0V      |

|------------------------------|------------|

| Reference VRT                | +4.3V      |

| Reference VRB                | +2.3V      |

| AVcc to DVcc                 | 0mV        |

| AGND to DGND                 | 0mV        |

| Analog Input V <sub>IN</sub> | 2 Vp-p max |

# THERMAL CHARACTERISTICS

|                                                   | DP |      |

|---------------------------------------------------|----|------|

| Thermal resistance, chip-to-case $\theta_{jc}$    | 20 | °C/W |

| Thermal resistance, chip-to-ambient $\theta_{jA}$ | 75 | °C/W |

|                                                   |    |      |

# SP973T8

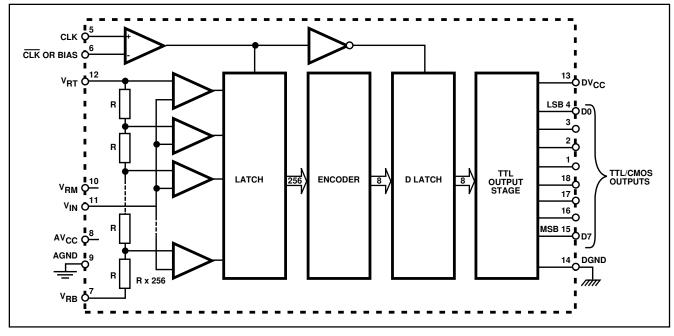

#### APPLICATION NOTES Analog Input Pin (Fig.3)

The analog input of the SP973T8 is connected to 256 comparators which have a combined capacitance of about 30pF. The sample/latch operation of the comparators causes the input capacitance to vary slightly as the comparator input transistors turn on/off. For this reason the input driver circuit should provide a low impedance signal to keep the harmonic distortion levels of the driver to a minimum.

The maximum amplitude of the analog input is defined by the setting of the two reference voltages V<sub>RT</sub> and V<sub>RB</sub>. Optimum performance will be obtained with the input signal biased midway between V<sub>RT</sub> and V<sub>RB</sub> with a peak to peak amplitude of V<sub>RT</sub>-V<sub>RB</sub>. The SP973T8 has excellent overload tracking of input signals with amplitudes greater than V<sub>RT</sub>-V<sub>RB</sub>, and will not be damaged if the absolute maximum ratings are adhered to.

Fig.3 One of 255 analog inputs connected to pin 11

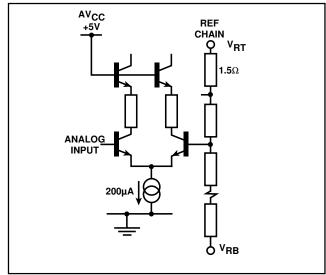

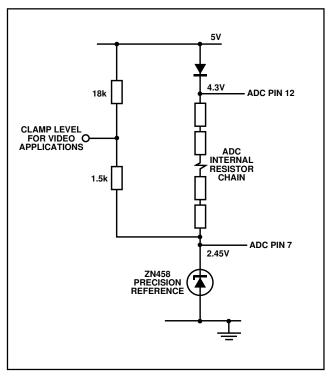

#### Voltage Reference Pins (Fig.4)

The SP973T8 converts analog signals in the range V<sub>RB</sub><V<sub>IN</sub><V<sub>RT</sub> into digital format, where V<sub>RB</sub> produces code 0 and V<sub>RT</sub> produces code 255. Between the pins V<sub>RT</sub> and V<sub>RB</sub> are a series of 256 resistors forming a reference chain with a total resistance of  $425\Omega$  (typically). The centre point of the reference chain is also connected to an external pin named V<sub>RM</sub> by which it is possible to provide precision trimming of the integral linearity of the device.

The maximum value of VRT is Vcc-0.7 volts since values above this figure will start to saturate the comparator, resulting in noticeable distortion. Optimum performance from a +5 Volt power supply is obtained with VRT<+4.3V and VRB a further 2 volts below VRT. In addition the VRT, VRB and VRM pins should be decoupled to ground close to the device pins using good quality 10nf capacitors. A simple method for providing the reference voltages is shown in Fig.4, and further information may be found in applications note AN72. With a reference ladder voltage of less than 2V the reduced LSB size causes a larger differential linearity error. Operation of the device below 1.5V may therefore cause missing codes.

Fig.4 Simple reference voltage generation

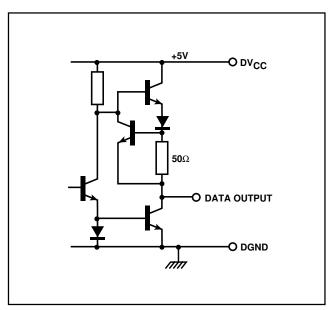

#### TTL/CMOS Outputs (Fig.5)

The data output levels of the SP973T8 are TTL/CMOS compatible and switch from 0V to +4V. The output circuit is capable of operation at clock frequencies in excess of 60MHz when driving into a standard LSTTL load.

Fig,5 TTL output stage

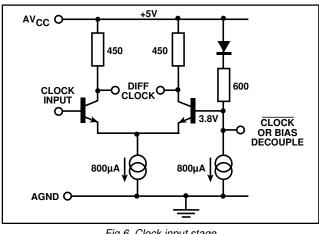

# Clock Input (Fig.6)

The SP973T8 will operate at clock frequencies up to and above 30MHz. The clock input has been designed to accept a 1Vpp signal, in either differential or single-ended mode, between the VIH(MAX) and VIL(MIN) levels indicated in the electrical specification. At VIH(MAX) or VIL(MIN) the CLK input will sink 800µÅ or source 3.2mÅ of current, respectively. (See Fig.6).

When used in single-ended operation, CLK may be decoupled to ground so that this input will then self-bias at approximately 1.2V below the supply Vcc. It may then be used to bias the CLK input, through a termination resistor, for ACcoupled applications as shown in Fig.8.

Alternatively a TTL level clock may be used by inserting an appropriate value resistor in series with the coupling capacitor.

Fig.6 Clock input stage

#### TIMING (Fig.7)

The analog input is sampled by the SP973T8 approximately 3ns (tab) after the falling edge of the clock. Due to the pipeline operation of the device, a further one clock cycle is required to produce the output data. As shown in Fig.7, the output has a good data valid time, enabling the data to be latched at both the rising and falling edges of the clock.

However, for clock frequencies above 25MHz the clock-tooutput delay time may lead to an inadequate data set up time relative to the rising clock edge and it is therefore recommended that the output data is latched on the falling clock edge.

Fig.7 Timing diagram

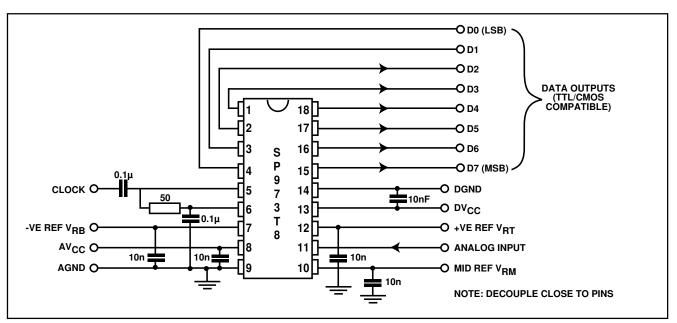

# **Circuit Board Construction (Fig.8)**

Excellent performance can be obtained from this ADC using only one solid ground plan for both analog and digital signals.

With all flash ADCs it is important to restrict digital crosstalk into the input, not only within the wanted signal bandwidth but also at frequencies between Nyquist and clock, as such signals will be aliased down into the wanted signal bandwidth.

We can give the designer two useful suggestions to reduce the above. First, due to the on-chip clock regeneration circuit, a low level clock can be fed to the ADC 1V p-p is recommended. The second suggestion is the addition of a small bead inductor in series with and close to the device analog input.

Supply line decoupling is very important when dealing with a mix of analog and digital signals as they can provide a source of digital feedback from the digital output currents. It is wise, therefore, to decouple the SP973T8 close to the device supply pins with good quality, high frequency, low inductance capacitors.

Due to the high clock rates involved, long clock lines to the device should be avoided to reduce the noise pick up.

Fig.8 Test/application circuit

HEADQUARTERS OPERATIONS GEC PLESSEY SEMICONDUCTORS Cheney Manor, Swindon, Wiltshire SN2 2QW, United Kingdom. Tel: (0793) 518000 Fax: (0793) 518411

#### GEC PLESSEY SEMICONDUCTORS

P.O. Box 660017 1500 Green Hills Road, Scotts Valley, California 95067-0017, United States of America. Tel: (408) 438 2900 Fax: (408) 438 5576

#### CUSTOMER SERVICE CENTRES

- FRANCE & BENELUX Les Ulis Cedex Tel: (1) 64 46 23 45 Fax : (1) 64 46 06 07

- GERMANY Munich Tel: (089) 3609 06-0 Fax : (089) 3609 06-55

- ITALY Milan Tel: (02) 66040867 Fax: (02) 66040993

- JAPAN Tokyo Tel: (03) 5276-5501 Fax: (03) 5276-5510

- NORTH AMERICA Integrated Circuits and Microwave Products Scotts Valley, USA Tel (408) 438 2900 Fax: (408) 438 7023.

- Hybrid Products, Farmingdale, USA Tel (516) 293 8686 Fax: (516) 293 0061.

- SOUTH EAST ASIA Singapore Tel: (65) 3827708 Fax: (65) 3828872

- SWEDEN Stockholm, Tel: 46 8 702 97 70 Fax: 46 8 640 47 36

- UK, EIRE, DENMARK, FINLAND & NORWAY

- Swindon Tel: (0793) 518510 Fax: (0793) 518582 These are supported by Agents and Distributors in major countries world-wide.

© GEC Plessey Semiconductors 1994 Publication No. DS2465 Issue No. 2.3 January 1994

This publication is issued to provide information only which (unless agreed by the Company in writing) may not be used, applied or reproduced for any purpose nor form part of any order or contract nor to be regarded as a representation relating to the products or services concerned. No warranty or guarantee express or implied is made regarding the capability, performance or suitability of any product or services. The Company in writing) may not be used, applied or reproduced for any purpose nor form part of any order or contract nor to be regarded as a representation relating to the products or services concerned. No warranty or guarantee express or implied is made regarding the capability, performance or suitability of any product or services. Information concerning possible methods of use is provided as a guide only and does not constitute any guarantee that such methods of use will be satisfactory in a specific piece of equipment. It is the user's responsibility to fully determine the performance and suitability of any equipment using such information and to ensure that any publication or data used is up to date and has not been superseded. These products are not suitable for use in any medical products whose failure to perform may result in significant injury or death to the user. All products and materials are sold and services provided subject to the Company's conditions of sale, which are available on request.